# Top-Gated Graphene Field-Effect Transistors with High Normalized Transconductance and Designable Dirac Point Voltage

Huilong Xu, Zhiyong Zhang,\* Haitao Xu, Zhenxing Wang, Sheng Wang, and Lian-Mao Peng\*

Key Laboratory for the Physics and Chemistry of Nanodevices and Department of Electronics, Peking University, Beijing 100871, China

raphene is considered as a promising material for high-performance nanoelectronics due to its extremely high carrier mobility, the ultimate thin body, and stability.<sup>1-5</sup> Because of the lack of an intrinsic band gap,<sup>2,3</sup> graphene is believed to be more suitable for radio frequency (RF) analog electronics,<sup>4,5</sup> instead of digital applications where a large current on/off ratio is required. Recently, graphene fieldeffect transistors (G-FETs) with a cutoff frequency ( $f_{\rm T}$ ) of up to 100–300 GHz were successively fabricated,<sup>6,7</sup> and their advantages for RF applications were amply demonstrated. Besides  $f_{T}$ , there are some other device parameters that are also important and need to be optimized. These parameters include transconductance and the working point of the device, that is, the Dirac point voltage. The transconductance of a transistor represents the amplifying ability which is very important for, among others, signal and power amplifier and frequency doubler applications,<sup>8–10</sup> and the Dirac point voltage will affect the dc supply voltage needed in real applications.<sup>8–10</sup> It is well-known that the quality of the gate oxide is one of the key factors determining the transconductance of a real device, and a high-quality dielectric layer is therefore highly desirable on pristine graphene which could lead to both high carrier mobility (less scatters) and large gate capacitance. Several dielectrics have been successfully grown on graphene via, for example, depositing functionalization and buffering layers to reduce scattering and retain high mobility, but the additional buffering layers significantly increase the effective thickness of the gate dielectric layer and reduce the gate oxide capacitance.<sup>11–18</sup> Very recently, an ultrathin yttrium oxide layer was grown

**ABSTRACT** High-performance graphene field-effect transistors (G-FETs) are fabricated with carrier mobility of up to 5400 cm<sup>2</sup>/V · s and top-gate efficiency of up to 120 (relative to that of back gate with 285 nm SiO<sub>2</sub>) simultaneously through growing high-quality Y<sub>2</sub>O<sub>3</sub> gate oxide at high oxidizing temperature. The transconductance normalized by dimension and drain voltage is found to reach 7900  $\mu$ F/V · s, which is among the largest of the published graphene FETs. In an as-fabricated graphene FET with a gate length of 310 nm, a peak transconductance of 0.69 mS/ $\mu$ m is realized, but further improvement is seriously hindered by large series resistance. Benefiting from highly efficient gate control over the graphene channel, the Dirac point voltage of the graphene FETs is shown to be designable *via* simply selecting a gate metal with an appropriate work function. It is demonstrated that the Dirac point voltage of the graphene FETs can be adjusted from negative to positive, respectively, *via* changing the gate material from Ti to Pd.

**KEYWORDS:** graphene · field-effect transistor · transconductance · Dirac point voltage

on graphene with an equivalent oxide thickness (EOT) of about 1.5 nm and an extremely large oxide capacitance of more than 2.2  $\mu$ F/cm<sup>2</sup>.<sup>19–21</sup> However, mobilities for both electron and hole were found to be lower than 2000 cm<sup>2</sup>/V·s.<sup>19–21</sup> It is the aim of this paper to report a simple annealing procedure that simultaneously yields a high carrier mobility of more than 5000 cm<sup>2</sup>/V·s and large gate capacitance of about 1.5  $\mu$ F/cm<sup>2</sup>.

Although it is well-known that the position of the Dirac point is affected by work function of the contact metal in back-gated graphene FETs,<sup>22</sup> few works focused on controlling the Dirac point of top-gated graphene FETs, which is another significant parameter for FET, similar to threshold voltage in conventional FETs. Similar to carbon nanotube FETs,<sup>23</sup> effective and stable doping is not easy in graphene, and the Dirac voltage of graphene FETs cannot thus be readily adjusted by tuning the dopant density of the graphene channel as in silicon

\* Address correspondence to zyzhang@pku.edu.cn, Impeng@pku.edu.cn.

Received for review March 24, 2011 and accepted April 29, 2011.

Published online April 29, 2011 10.1021/nn201115p

© 2011 American Chemical Society

VOL.5 • NO.6 • 5031-5037 • 2011

MOSFETs.<sup>24</sup> Alternatively, the Dirac point of a graphene device may be adjusted by selecting a gate metal with suitable work function, but an important precondition for realizing this potential is to have a large gate capacitance to ensure a strong coupling between the gate electrode and graphene channel.

In this paper, we fabricated a high-performance graphene FET with a carrier mobility of up to 5400  $\text{cm}^2/\text{V} \cdot \text{s}$  and a top-gate relative efficiency of up to 120 (relative to the back gate with 285 nm  $SiO_2$ ) simultaneously, leading to a normalized transconductance (by dimension and drain voltage) as large as 7900  $\mu$ F/V·s, which is among the largest in the published devices. In an as-fabricated graphene FET with a 310 nm gate length, a peak transconductance as high as 0.69 mS/ $\mu$ m is realized. One of the important merits of a highly efficient gate control over the graphene channel is further demonstrated by using gate metals with appropriate work functions to adjust the Dirac point voltage of the graphene FETs. It is shown that using titanium instead of palladium as gate metal the Dirac point voltage of the graphene FETs can be adjusted from negative to positive, respectively; that is, the type of charged carriers in the channel at zero gate voltage can be shifted from electrons to holes.

### **RESULTS AND DISCUSSION**

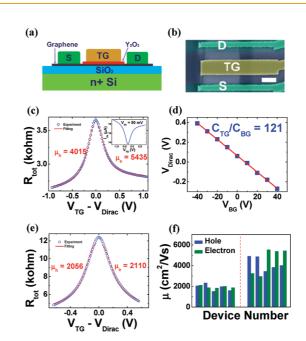

Figure 1a shows the structure of the top-gated graphene FET, and Figure 1b shows the SEM picture of an as-fabricated device in which the graphene channel is covered by a gate of about 1  $\mu$ m in length and 2.7  $\mu$ m in width. In order to improve the quality of the Y<sub>2</sub>O<sub>3</sub> gate insulator, the yttrium (Y) film was oxidized at 270 °C, which is higher than the previously used oxidization temperature of 180  $^\circ\text{C}.^{19-21}$  To avoid possible deformation of graphene caused by O2 at high temperature,<sup>25</sup> the oxidization temperature was therefore chosen to be less than 300 °C. In order to extract the carrier mobility using the diffusive model, devices used in this work were fabricated with a relatively long gate length of about 1.0  $\mu$ m. A typical transfer characteristic measured from such a device is shown as the inset of Figure 1c at a bias of 50 mV; from this curve, the relation between total resistance and top-gate voltage was then obtained and is shown in Figure 1c. The device is a typical ambipolar FET as manifested by the "V" shape gate dependence of the transfer characteristics on the gate voltage. To extract carrier mobility from transfer characteristics, the oxide capacitance of the top gate must be obtained at first. Since the graphene channel can be simultaneously controlled by top gate and back gate, the shift in the top-gate Dirac point voltage  $V_{TG,Dirac}$  is linearly dependent on the change of the back-gate voltage  $V_{BG}$  as shown in Figure 1d. The inverse of the slope of the  $V_{TG,Dirac} - V_{BG}$ line is 121, which is determined by the ratio between

Figure 1. Electrical characteristics of graphene FETs. (a) Cross section diagram of the graphene FETs. (b) SEM image of an as-fabricated device. The channel length is about 2.6  $\mu$ m, and gate length is about 1  $\mu$ m. Scale bar: 1  $\mu$ m. (c) Total resistance of the device under drain voltage of 50 mV. The blue circles show the experiment data with respect to Dirac point voltage; the red lines are theoretical fittings for hole and electron branches. The inset shows the as-measured drain current as a function of gate voltage. (d) Top-gate Dirac point voltage as a function of back-gate voltage. (e) Total resistance of a similar graphene FET with the dielectric being grown at 180 °C. (f) Statistics of carrier mobility of graphene FETs. Mobility of graphene FETs with  $Y_2O_3$  dielectric layer formed at 180 °C is shown at the left side of the red dashed line; the right side shows mobility of graphene FETs with Y<sub>2</sub>O<sub>3</sub> dielectric layer formed at 270 °C.

the top-gate oxide capacitance and back-gate capacitance of unit area, and is independent of the quantum capacitance of graphene, that is,  $C_{OX}/C_{BG} = -\Delta V_{BG}/$  $\Delta V_{\text{TG}}$ .<sup>13,15,16,19,20</sup> Using a relative dielectric constant of 3.9 and a thickness of 285 nm for the back-gate silicon dioxide, which yields a back-gate capacitance 0.0121  $\mu$ F/cm<sup>2</sup>, the top-gate capacitance is derived to be 1.46  $\mu$ F/cm<sup>2</sup>. The value of top-gate capacitance can also be estimated by using the conventional capacitance equation,  $C_{OX} = \kappa \varepsilon_0 / t_{OX}$ . For the Y<sub>2</sub>O<sub>3</sub> film in the G-FET of Figure 1d, the oxide thickness  $t_{OX}$  is 6 nm (as measured by AFM) and the relative dielectric constant  $\kappa \approx 10^{20}$  We then obtain  $C_{OX} = 1.48 \ \mu \text{F/cm}^2$ , which is very close to the value of 1.46  $\mu$ F/cm<sup>2</sup> that we just obtained. The electron mobility  $\mu_{e}$  and hole mobility  $\mu_{h}$ of the device are then extracted using the previously reported model<sup>14</sup>

$$R_{\text{total}} = R_{\text{s}} + \frac{L_{\text{G}}}{W} \frac{1}{e\mu\sqrt{n_0^2 + n^2}}$$

(1)

where  $R_{\text{total}} = V_{\text{ds}}/I_{\text{ds}}$  is the total resistance of the graphene FET including the series resistance  $R_{\text{s}}$  and the ideal channel resistance modulated by the top gate;  $L_{\text{G}}$  is the length of the top gate, and W is the width

VOL.5 • NO.6 • 5031-5037 • 2011

agnanc www.acsnano.org of the graphene channel covered by the top gate; n and  $n_0$  are the top-gate-modulated carrier density and the residual density, respectively, and e is the electron charge. The capacitive carrier density *n* is related to the gate voltage via the equation

$$V_{\text{TG}} - V_{\text{TG}, \text{Dirac}} = \frac{ne}{C_{\text{OX}}} + \frac{\hbar v_{\text{F}} \sqrt{\pi n}}{e}$$

(2)

where the first term on the right-hand side of eq 2 describes the carrier density induced by the top gate via C<sub>OX</sub>, the second term describes the effect of quantum capacitance in graphene, and the Fermi velocity  $v_{\rm F} = 1.15 \times 10^6$  m/s.<sup>3,18,20,26</sup> lt should be noted that the p-type branch and n-type branch are always asymmetric at two sides of the Dirac point in our devices, which was observed also in previous works<sup>27-31</sup> and attributed to the pinning of charge density below the contact metal<sup>27,28</sup> and the conductance suppression of only one carrier type induced by long-range scatters at the interface of the oxide/graphene.<sup>29-33</sup> Because of the conductance asymmetry, the hole branch and electron branch in the transfer characteristic are fitted separately using eqs 1 and 2, and corresponding hole and electron mobilities are extracted. The fitting yields a mobility of 4000  $\text{cm}^2/\text{V}\cdot\text{s}$  for holes and 5400 cm<sup>2</sup>/V·s for electrons. The improved carrier mobility relative to previous G-FETs<sup>19-21</sup> with Y<sub>2</sub>O<sub>3</sub> gate insulator is largely benefited from the use of higher oxidization temperature. Since the charged traps originated from defects will decrease with increasing oxidation temperature, scattering then decreases, leading to higher carrier mobility. Figure 1e gives the transfer characteristic of a typical G-FET with Y<sub>2</sub>O<sub>3</sub> insulator oxidized at 180 °C, from which the carrier mobilities are extracted, which are, respectively, 2056 and 2110  $\text{cm}^2/\text{V}\cdot\text{s}$  for electrons and holes. To ensure the effect of oxidizing temperature on the quality of the Y<sub>2</sub>O<sub>3</sub> insulator, we compared the carrier mobility between two groups of G-FETs in Figure 1f with the  $Y_2O_3$  being formed at different oxidizing temperature. The carrier mobility ranges from 1500 to 2000 cm<sup>2</sup>/V·s for the G-FETs fabricated with  $Y_2O_3$ oxidized at 180 °C, which increases to about  $3000-5500 \text{ cm}^2/\text{V} \cdot \text{s}$  for the G-FETs being fabricated with Y<sub>2</sub>O<sub>3</sub> oxidized at 270 °C. The carrier mobility is thus seen (Figure 1f) to have been improved significantly both for electrons and holes simply via increasing the oxidization temperature from 180 to 270 °C.

Compared to the previously reported data, our graphene FET preserves both high mobility and gate efficiency, which in turn leads to high transconductance of a graphene device. Transconductance is the key device parameter which characterizes the amplifying ability of a FET device and is especially important for analog applications. It is well-known that the transconductance of a G-FET is dependent on its dimension and the source drain bias voltage. Although

**TABLE 1.** Comparison of Maximum Carrier Mobility and Gate Oxide Capacitance between Our Device and Other Published Graphene FETs (Data for Devices A-F Were Taken from References 13–18)

|                                     | $\mu$ (cm²/V $\cdot$ s) | <b>С<sub>тб</sub> (µF/cm²)</b> | μ <b>ር<sub>τς</sub> (μF/V・s)</b> |

|-------------------------------------|-------------------------|--------------------------------|----------------------------------|

| device A <sup>13</sup> (Columbia)   | 1200                    | 0.552                          | 662                              |

| device B <sup>14</sup> (UT, Austin) | 8600                    | 0.306                          | 2632                             |

| device C <sup>15</sup> (IBM)        | 7700                    | 0.184                          | 1417                             |

| device D <sup>16</sup> (UCLA)       | 23600                   | 0.164                          | 3870                             |

| device E <sup>17</sup> (HRL)        | 6000                    | 0.170                          | 1020                             |

| device F <sup>18</sup> (Manchester) | 10000                   | 0.470                          | 4700                             |

| this work                           | 5400                    | 1.462                          | 7895                             |

many G-FETs with large transconductance normalized only by channel width were reported,<sup>13–18</sup> a fair comparison between different devices is still absent since these devices were measured at different source/ drain bias and channel length or electrical field. Unlike in conventional FETs, current saturation is not usually observable in graphene FETs and transconductance generally increases with increasing bias. Here we propose to use a normalized transconductance, by both channel width and field, to benchmark the amplifying ability of graphene FETs. For a FET with a long enough channel and in its linear working region,<sup>24</sup> transport of the device can be described using a drift-diffusion model, and the intrinsic transconductance can be written as

$$g_{\rm m} = \mu C_{\rm TG} \frac{W}{L_{\rm G}} V_{\rm ds} \tag{3}$$

in which W and  $L_G$  are, respectively, the width and length of the gate,  $C_{TG}$  is the gate capacitance, and  $\mu$  is the carrier mobility. Normalized by the dimension and bias of the device, the transconductance is then related directly to the product of carrier mobility and gate capacitance

$$g_{\rm mN} = g_{\rm m} \frac{L_{\rm G}}{WV_{\rm ds}} = \mu C_{\rm TG} \tag{4}$$

that is, the product of mobility and gate capacitance is a universal parameter for benchmark of the amplifying potential of graphene FETs with different dimensions and under various work voltages. Here we thus call it normalized transconductance. It should be noted that  $C_{TG}$  is the total capacitance due to two capacitors connected in series, that is, the oxide capacitor of the gate oxide and quantum capacitor of the graphene channel. It should be noted that the quantum capacitance of graphene is dependent on gate voltage and is usually much larger than the oxide capacitance especially at bias far from the Dirac point. As a simple approximation, therefore, we substitute  $C_{TG}$  with  $C_{OX}$ in eq 4. Table 1 lists three parameters including carrier mobility, gate capacitance, and normalized transconductance for our and other published high-performance G-FETs.<sup>13–18</sup> Although the mobility of our G-FET is not

VOL.5 • NO.6 • 5031-5037 • 2011

extremely high, the normalized transconductance can reach up to about 7900  $\mu$ F/V·s, among the largest of the published graphene FETs.<sup>34</sup> The high normalized transconductance indicates the overall high efficiency of graphene channel and gate oxide. This normalized transconductance value suggests that, for a G-FET with a gate length of 1  $\mu$ m and a bias of 1.0 V, its transconductance could reach up to 7.9 mS/ $\mu$ m, which is far above all of the published results for G-FETs with shorter gate length and larger bias voltage.<sup>13–19,35,36</sup> Except for the graphene channel and gate insulator, the series resistances including access resistance (from the graphene channel between top-gate and source/ drain electrode) and contact resistance would also play an important role in G-FETs;<sup>36–38</sup> in particular, a large series resistance will seriously degrade the actual transconductance.

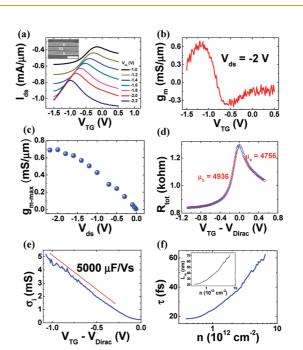

In general, the combination of high mobility and high gate efficiency will lead to a high transconductance in G-FETs. According to eq 3, the transconductance of a G-FET is inversely proportional to gate length  $L_{G}$ . The transconductance of the G-FET can thus be further improved by scaling down the gate length in graphene FETs. The process of fabricating G-FET with submicrometer channel and gate length is basically the same as mentioned above, but with a slight difference in the choice of source and drain contact metals. Here a more complex Ti/Pd/Au (1/20/30 nm) structure is used, aiming to further decrease the contact resistance.<sup>6</sup> Shown in Figure 2a are transfer characteristics of a graphene FET with gate length of about 310 nm and spacing between the top-gate electrode and source/drain contacts of about 100 nm. The onstate current reaches up to 1 mA/ $\mu$ m, which is among the largest in all reported graphene FETs.<sup>6,7,9,13-18</sup> The small  $I_{\rm op}/I_{\rm off}$  ratio of about 1.5 can be attributed to the relatively low fraction ( $\sim$ 0.6) of the gate-modulated channel length compared to the total channel length. Figure 2b shows the transconductance per channel width, which is seen to strongly depend on the gate voltage owing to the impact of series resistance.<sup>15,36,37</sup> The peak transconductance is also dependent on source/drain bias, as shown in Figure 2c, which reaches up to 0.69 mS/ $\mu$ m at a bias of -2.0 V. This value is the largest observed in all non-self-aligned graphene FETs<sup>6,9,10,13-18</sup> and is about two times better than the silicon transistor with similar gate length.<sup>39</sup> To estimate the mobility and series resistance of this device, the  $V_{TG}$ dependent total resistance of the device is measured at low bias of 50 mV and shown in Figure 2d. The  $R_{\text{total}} - V_{\text{TG}}$  curve is fitted using eq 1, yielding a hole mobility of 4936 cm<sup>2</sup>/V·s (the corresponding normalized transconductance is about 7000  $\mu$ F/V  $\cdot$  s) and series resistance  $R_s$  of 815  $\Omega$ . Although a high peak transconductance of up to 0.69 mS/ $\mu$ m is achieved, the corresponding normalized transconductance is only about 45  $\mu$ F/V · s, which it is much lower than its intrinsic value

Figure 2. Electrical characteristics of a short channel graphene FET. (a) Transfer characteristics of a graphene FET with  $L_G = 310$  nm at different drain bias. Inset shows the SEM image of the graphene FET. Scale bar: 1  $\mu$ m. (b) Transconductance of the device as a function of top-gate voltage under a bias of -2.0 V and (c) peak transconductance of the graphene FET as a function of drain voltage. (d) Total resistance of the device as a function of gate voltage under drain voltage of 50 mV. The blue circles show the experiment data with respect to the Dirac point voltage; the red lines are theoretical fittings. (e) Gate-voltage-dependent conductivity of the channel after subtracting the series resistance. The slope of the curve is related to the normalized transconductance. (f) Scattering time as a function of carrier concentration in the G-FET. Inset shows carrier concentration-dependent mean-free-path length.

of 7000  $\mu$ F/V·s. The tremendous gap between the actual normalized transconductance and the expected value results mainly from the existence of the large series resistance in the graphene channel which cannot be modulated by the top gate. If we subtract the series resistance via  $R_{intrinsic} = R_{total} - R_s$  from the experimental data of Figure 2d, the conductance of the device is shown to follow  $V_{TG}$  almost linearly (Figure 2e), and the slope is just the normalized transconductance. It should be noted that the series resistance  $R_s$  is treated as a fixed value here. Since  $R_s$ originates from the part of the channel that is ungated by the top gate and contacts, it is, in general, dependent on the bias of the back gate<sup>14</sup> and nearly independent of the top gate. Since, in the device of Figure 2d, back gate is not used, it is reasonable to consider R<sub>s</sub> as a fixed value. Then after eliminating the effect of series resistance, the normalized transconductance is recovered up to about 5000  $\mu$ F/V·s, which is close to the intrinsic value of about 7000  $\mu$ F/V·s, with the remaining difference being mainly a result from the effect of quantum capacitance. Therefore, the peak transconductance can be significantly improved through

VOL.5 • NO.6 • 5031-5037 • 2011

IAI

www.acsnano.org

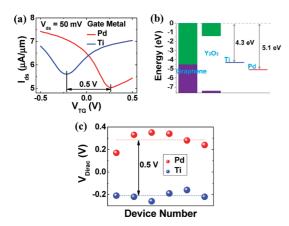

Figure 3. Dirac point voltages of graphene FETs with different top gate metals. (a) Transfer characteristics of two different devices with Ti and Pd being the gate metal. (b) Work function comparisons between graphene and Ti/Pd metal. (c) Statistics on the Dirac point voltage of 12 devices with Ti or Pd being gate metals.

decreasing the series resistance, which could be achieved by optimizing the contact and adopting a self-aligned gate structure to decrease access resistance. Very recently, G-FETs with ultrahigh transconductance were fabricated with self-aligned gate, and the major progress comes mainly with significantly lowered access resistance.<sup>7</sup> It should be noted that here the carrier mobility and series resistance of the G-FET are calculated using eq 1, which is based on the validity of the diffusive transport model, and we now consider the validity of using the diffusive model in our G-FET. The scattering time  $\tau$  and mean-free-path length (MFP length)  $L_{\rm m}$  of carriers are estimated as<sup>30</sup>  $\tau = \sigma (\pi/n)^{1/2} \times \hbar/(e^2 \nu_F)$  and  $L_m = \nu_F \tau$ . The results are shown in Figure 2f. The MFP length is seen to increase with increasing carrier density but is smaller than 60 nm for relatively high  $n = 6 \times 10^{12}$ /cm<sup>2</sup> and is about 1/5 of the gate length. It is thus justified to use the diffusive transport model to analyze the results obtained from our G-FET.

The Dirac point voltage will affect the dc supply voltage needed in real applications and therefore is a significant parameter for G-FET operation. Similar to carbon nanotube FETs,<sup>23</sup> the Dirac point voltage of a G-FET cannot be readily adjusted by tuning the dopant density of the graphene channel as routinely done in silicon MOSFETs. This is because stable and controlled doping in graphene is difficult.<sup>24</sup> Benefiting from the excellent gate control over the graphene channel in our devices with ultrahigh gate capacitance, the Dirac point voltage can be adjusted by selecting appropriate gate metal with suitable work function. Figure 3a shows two typical transfer characteristics measured from two devices with a Ti and Pd gate. Typical hysteretic characteristics of the devices are given in the Supporting Information, which shows that only a 10 mV hysteresis exists when sweeping the top-gate voltage from -0.5 to 0.5 V and then backward. The Dirac point

voltage  $V_{\text{Dirac}}$  is -0.22 V for the G-FET with a Ti gate, which increases to 0.27 V when using Pd as gate metal. A shift of up to 0.49 V in the Dirac point voltage is realized simply by changing the gate metal. At zero gate voltage, the device with a Ti gate is electron accumulated, and the device with a Pd gate is hole accumulated. This is in qualitative agreement with the work function difference between the gate metals. As shown in Figure 3b, the work function of Ti (W = 4.3 eV) is smaller than that of graphene (4.5 eV); that is, the Fermi level of Ti is higher than that of graphene, then the Fermi level of graphene will be raised after intimately contacting with the Ti gate through Y<sub>2</sub>O<sub>3</sub> film as a media, and the channel would be electron accumulated. On the other hand, Pd (W = 5.1 eV) gate has a lower Fermi level than graphene, then the graphene channel would be a hole conductive one. The gate metal work function induced  $V_{\text{Dirac}}$  change is further manifested in the statistic results on 12 G-FETs (Figure 3c), among which 6 devices are fabricated with a Ti gate and the others with a Pd gate. For the devices with a Pd gate, the Dirac point voltage varies from 0.18 to 0.35 V, while for the devices with a Ti gate, the Dirac point voltage varies from -0.15 to -0.25 V. There exists clearly a gap between the two groups of devices, and the statistical Dirac point voltage shift here is about 0.5 V, which is smaller than the work function difference of 0.8 eV between Ti and Pd. This large discrepancy is largely due to the fact that the work function of a metal on a real dielectric is different from that in vacuum. As a rule, the effective work function difference between different metals on a dielectric is smaller than that in vacuum.<sup>40,41</sup> The ratio between the effective work function difference for different metals on a dielectric to that in vacuum is measured by a S parameter that accounts for dielectrics screening and depends on the electronic component of the dielectric constant<sup>40,41</sup>

$$\Phi_{\mathsf{M},\mathsf{eff}} = \Phi_{\mathsf{CNL},\mathsf{d}} + \mathsf{S}(\Phi_{\mathsf{M},\mathsf{vac}} - \Phi_{\mathsf{CNL},\mathsf{d}})$$

(5)

where  $\Phi_{\text{M,eff}}$  is the effective work function of metal in dielectric,  $\Phi_{\text{CNL,d}}$  is the charge neutrality level of the dielectric, and  $\Phi_{\text{M,}\nu\text{ac}}$  is the work function of metal in vacuum. Thus we have

$$\Delta \Phi_{M,eff} = S \Delta \Phi_{M,vac}$$

(6)

Since  $\Delta \Phi_{M,eff}$  and  $\Delta \Phi_{M,vac}$  are about 0.5 and 0.8 eV, respectively, we therefore obtain  $S \sim 0.6$  for the metals on  $Y_2O_3$  with a dielectric constant of about 10.

## CONCLUSION

In conclusion, high-performance top-gated graphene FETs (G-FETs) have been fabricated with ultrahigh gate efficiency of up to 120 (relative to the back gate with 285 nm SiO<sub>2</sub>) *via* optimizing thermal oxidation of  $Y_2O_3$

agnanc www.acsnano.org top-gate oxide. The carrier mobility in the graphene channel is significantly improved to more than 5000 cm<sup>2</sup>/V·s, and the transconductance normalized by dimension and drain voltage is increased to 7900  $\mu$ F/V·s, which is among the largest of the published graphene FETs. In an as-fabricated G-FET with  $L_{\rm G} = 310$  nm, a peak transconductance of up to 0.69 mS/ $\mu$ m is reached, and which may in principle be further improved by reducing the series resistance of the device. As a result of the extremely

efficient gate control over the graphene channel, the Dirac point voltage of the graphene FET is shown to be designable simply by selecting suitable gate metal with appropriate work function. It is found that when changing the gate electrode from Ti to Pd the Dirac point voltage of the graphene FET can be adjusted from negative to positive, or namely, the majority of carriers in the channel at quasi-equilibrium can be changed from electrons to holes.

#### METHODS

Single-layer graphene samples were derived by mechanical cleavage of Kish graphite and deposited on a n-doped Si substrate with a 285 nm thermal SiO<sub>2</sub>. Single-layer graphene samples were identified by optical contrast and Raman spectroscopy. The device fabrication is generally a gate-first process. First, a thin yttrium metal film was deposited on specific area of graphene using E-beam lithography and E-beam evaporation followed by a lift-off process. Second, an yttrium oxide layer was formed by oxidizing the yttrium film on a hot plate at 270 °C for 5 min or 180 °C for 10 min. Additional forming gas (Ar/H<sub>2</sub> = 5:1) annealing was carried out in a furnace at 300 °C for 1 h in order to improve the quality of the Y2O3 layer. Third, source/drain contacts were fabricated by E-beam lithography and E-beam evaporation followed by a lift-off process. Without specific notification, the contact metal is Ti/Au (50 nm/10 nm). Last, a 60 nm titanium or palladium gate metal was fabricated similarly to that of source/drain contacts. The device was then tested in vacuum at room temperature using a Keithley 4200 semiconductor analyzer and a probe station (Lakeshore TTP-4).

Acknowledgment. This work was supported by the Ministry of Science and Technology of China (Grant Nos. 2011CB933001 and 2011CB933002), the Fundamental Research Funds for the Central Universities, and National Science Foundation of China (Grant No. 61071013).

*Supporting Information Available:* Additional experimental details. This material is available free of charge *via* the Internet at http://pubs.acs.org.

#### **REFERENCES AND NOTES**

- Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonors, S. V.; Grigorieva, I. V.; Firsov, A. A. Electric Field Effect in Atomically Thin Carbon Films. *Science* 2004, 306, 666–669.

- 2. Geim, A. K.; Novoselov, K. L. The Rise of Graphene. *Nat. Mater.* **2007**, *6*, 183–191.

- Castro Neto, A. H.; Guinea, F.; Peres, N. M. R.; Novoselov, K. S.; Geim, A. K. The Electronic Properties of Graphene. *Rev. Mod. Phys.* 2009, *81*, 109–162.

- Schwierz, F. Graphene Transistor. Nat. Nanotechnol. 2010, 5, 487–496.

- Avouris, Ph. Graphene: Electronic and Photonic Properties and Devices. Nano Lett. 2010, 10, 4285–4294.

- Lin, Y.-M.; Dimitrakopoulos, C.; Jenkins, K. A.; Farmer, D. B.; Chiu, H.-Y.; Grill, A.; Avouris, Ph. 100-GHz Transistors from Wafer-Scale Epitaxial Graphene. *Science* **2010**, *327*, 662–662.

- Liao, L.; Lin, Y.-C.; Bao, M.; Cheng, R.; Bai, J.; Liu, Y.; Qu, Y.; Wang, K. L.; Huang, Y.; Duan, X. High-Speed, Graphene Transistors with a Self-Aligned Nanowire Gate. *Nature* 2010, 467, 305–308.

- Yang, X.; Liu, G.; Balandin, A. A.; Mohanram, K. Triple-Mode Single-Transistor Graphene Amplifier and Its Applications. *ACS Nano* 2010, *4*, 5532–5538.

- Wang, H.; Nezich, D.; Kong, J.; Palacios, T. Graphene Frequency Multipliers. *IEEE Electron Device Lett.* 2009, 30, 547–549.

- Wang, Z. X.; Zhang, Z. Y.; Xu, H. L.; Ding, L.; Wang, S.; Peng, L.-M. A High-Performance Top-Gate Graphene Field-Effect Transistor Based Frequency Doubler. *Appl. Phys. Lett.* 2010, *96*, 173104.

- Wang, X. R.; Tabakman, S. M.; Dai, H. J. Atomic Layer Deposition of Metal Oxides on Pristine and Functionalized Graphene. J. Am. Chem. Soc. 2008, 130, 8152–8153.

- Lee, B. K.; Park, S.-Y.; Kim, H.-C.; Cho, K. J.; Vogel, E. M.; Kim, M. J.; Wallace, R. M.; Kim, J. Y. Conformal Al<sub>2</sub>O<sub>3</sub> Dielectric Layer Deposited by Atomic Layer Deposition for Graphene-Based Nanoelectronics. *Appl. Phys. Lett.* **2008**, *92*, 203102.

- Meric, I.; Han, M. Y.; Young, A. F.; Ozyilmaz, B.; Kim, P.; Shepard, K. L. Current Saturation in Zero-Bandgap, Top-Gated Graphene Field-Effect Transistors. *Nat. Nanotechnol.* 2008, 3, 654–659.

- Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S. Realization of a High Mobility Dual-Gated Graphene Field-Effect Transistor with Al<sub>2</sub>O<sub>3</sub> Dielectric. *Appl. Phys. Lett.* **2009**, *94*, 062107.

- Farmer, D. B.; Chiu, H.-Y.; Lin, Y.-M.; Jenkins, K. A.; Xia, F. N.; Avouris, P. Utilization of a Buffered Dielectric To Achieve High Field-Effect Carrier Mobility in Graphene Transistors. *Nano Lett.* **2009**, *9*, 4474–4478.

- Liao, L.; Bai, J. W.; Qu, Y. Q.; Lin, Y. C.; Li, Y. J.; Huang, Y.; Duan, X. F. High- A Oxide Nanoribbons as Gate Dielectrics for High Mobility Top-Gated Graphene Transistors. *Proc. Natl. Acad. Sci. U.S.A.* 2010, 107, 6711–6715.

- Moon, J. S.; Curtis, D.; Bui, S.; Hu, M.; Gaskill, D. K.; Tedesco, J. L.; Asbeck, P. A.; Jernigan, G. G.; VanMil, B. L.; Myers-Ward, R. L.; *et al.* Top-Gated Epitaxial Graphene FETs on Si-Face SiC Wafers with a Peak Transconductance of 600 mS/mm. *IEEE Electron Device Lett.* **2010**, *31*, 260–262.

- Ponomarenko, L. A.; Yang, R.; Gorbachev, R. V.; Blake, P.; Katsnelson, M. I.; Novoselov, K. S.; Geim, A. K. Density of States and Zero Landau Level Probed through Capacitance of Graphene. *Phys. Rev. Lett.* **2010**, *108*, 136801.

- Wang, Z. X.; Xu, H. L.; Zhang, Z. Y.; Wang, S.; Ding, L.; Zeng, Q. S.; Yang, L. J.; Pei, T.; Liang, X. L.; Gao, M.; *et al.* Growth and Performance of Yttrium Oxide as a Perfect High-κ Gate Dielectric for Carbon-Based Electronics. *Nano Lett.* **2010**, *10*, 2024–2030.

- Xu, H. L.; Zhang, Z. Y.; Wang, Z. X.; Wang, S.; Liang, X. L.; Peng, L.-M. Quantum Capacitance Limited Vertical Scaling of Graphene Field Effect Transistor. ACS Nano 2011, 5, 2340–2347.

- Xu, H. L.; Zhang, Z. Y.; Peng, L. M. Measurements and Microscopic Model of Quantum Capacitance in Graphene. *Appl. Phys. Lett.* 2011, *98*, 133122.

- Park, N.; Kim, B.-Y.; Lee, J.-O; Kim, J.-J. Influence of Metal Work Function on the Position of the Dirac Point of Graphene Field-Effect Transistors. *Appl. Phys. Lett.* 2009, 95, 243105.

- Zhang, Z. Y.; Wang, S.; Ding, L.; Liang, X. L.; Pei, T.; Shen, J.; Xu, H. L.; Chen, Q.; Cui, R. L.; Li, Y.; *et al.* Self-Aligned Ballistic

VOL.5 • NO.6 • 5031-5037 • 2011

n-Type Single-Walled Carbon Nanotube Field-Effect Transistors with Adjustable Threshold Voltage. *Nano Lett.* **2008**, *8*, 3696–3701.

- 24. Sze, S. *Physics of Semiconductor Devices*; Wiley: New York, 1981.

- Ryu, S.; Liu, L.; Berciaud, S.; Yu, Y. J.; Liu, H.; Kim, P.; Flynn, G. W.; Brus, L. E. Atmospheric Oxygen Binding and Hole Doping in Deformed Graphene on a SiO<sub>2</sub> Substrate. *Nano Lett.* **2010**, *10*, 4944–4951.

- Zhang, Y. B.; Tan, Y.-W.; Stormer, H. L.; Kim, P. Experimental Observation of the Quantum Hall Effect and Berry's Phase in Graphene. *Nature* **2005**, *438*, 201–204.

- Huard, B.; Stander, N.; Sulpizio, J. A.; Goldhaber-Gordon, D. Evidence of the Role of Contacts on the Observed Electron–Hole Asymmetry in Graphene. *Phys. Rev. B* 2008, *78*, 121402.

- 28. Nouchi, R.; Shiraishi, M.; Suzuki, Y. Transfer Characteristics in Graphene Field-Effect Transistors with Co Contacts. *Appl. Phys. Lett.* **2008**, *93*, 152104.

- Farmer, D. B.; Golizadeh-Mojarad, R.; Pereheinos, V.; Lin, Y.-M.; Tulevski, G. S.; Tsang, J. C.; Avouris, Ph. Chemical Doping and Electron–Hole Conduction Asymmetry in Graphene Devices. *Nano Lett.* **2009**, *9*, 388–392.

- Tan, Y.-W.; Zhang, Y.; Bolotin, K.; Zhao, Y.; Adam, S.; Hwang, E. H.; Sarma, S. D.; Stormer, H. L.; Kim, P. Measurement of Scattering Rate and Minimum Conductivity in Graphene. *Phys. Rev. Lett.* **2007**, *99*, 246803.

- Chen, J. H.; Jang, C.; Adam, S.; Fuhrer, M. S.; Williams, E. D. Charged-Impurity Scattering in Graphene. *Nat. Phys.* 2008, 4, 377–381.

- Adam, S.; Wang, E. H.; Galitski, V. M.; Darma, S. D. A Self-Consistent Theory for Graphene Transport. *Proc. Natl. Acad. Sci. U.S.A.* 2007, 104, 18392–18397.

- Hwang, E. H.; Adam, S.; Sarma, S. D. Carrier Transport in Two-Dimensional Graphene Layers. *Phys. Rev. Lett.* 2007, 98, 186806.

- 34. Efetov, D. K.; Kim, P. Controlling Electron–Phonon Interactions in Graphene at Ultrahigh Carrier Densities. *Phys. Rev. Lett.* **2010**, *105*, 256805.

- Liao, L.; Bai, J.; Cheng, R.; Lin, Y.-C.; Jiang, S.; Qu, Y.; Huang, Y.; Duan, X. Sub-100 nm Channel Length Graphene Transistors. *Nano Lett.* **2010**, *10*, 3952–3956.

- 36. Lin, Y.-M.; Chiu, H.-Y.; Jenkins, K. A.; Farmer, D. B.; Avouris, Ph. Dual-Gate Graphene FETs with  $f_{\rm T}$  of 50 GHz. *IEEE Electron Device Lett.* **2010**, *31*, 68–70.

- Farmer, D. B.; Lin, Y.-M.; Avouris, Ph. Graphene Field-Effect Transistors with Self-Aligned Gates. *Appl. Phys. Lett.* 2010, *97*, 013103.

- Nagashio, K.; Nishimura, T.; Kita, K.; Toriumi, A. Metal/ Graphene Contact as a Performance Killer of Ultra-high Mobility Graphene—Analysis of Intrinsic Mobility and Contact Resistance. *IEEE International Electron Devices Meeting*, 2009, 5424297, Baltimore, MD.

- Taur, Y.; Buchanan, D. A.; Chen, W.; Frank, D. J.; Ismail, K. E.; LO, S.; Sai-Halasz, G. A.; Viswanathan, R. G.; Wann, H. C.; Wind, S. J.; *et al.* CMOS Scaling into the Nanometer Regime. *Proc. IEEE* **1997**, *85*, 486–504.

- Yeo, Y. C.; Ranade, P.; King, T. J.; Hu, C. M. Effects of High-k Gate Dielectric Materials on Metal and Silicon Gate Workfunctions. *IEEE Electron Device Lett.* 2002, 23, 342–344.

- Robertson, J. High Dielectric Constant Gate Oxides for Metal Oxide Si Transistors. *Rep. Prog. Phys.* 2006, 69, 327– 396.